#### International Journal of Emerging Trends in Computer Science and Information Technology

ISSN: 3050-9246 | https://doi.org/10.63282/30509246/IJETCSIT-V4I3P102 Eureka Vision Publication | Volume 4, Issue 3, 11-22, 2023

Original Article

# Memory Hierarchy Optimization Strategies for High-Performance Computing Architectures

Krunali Patel Sardar Vallabhbhai National Institute of Technology, Surat, Gujarat, India.

Abstract - In High-Performance Computing (HPC) architectures, optimizing memory hierarchy is crucial for enhancing system performance and efficiency. The memory hierarchy consists of various levels of storage, each with distinct characteristics in terms of speed, cost, and capacity. As the gap between processor speeds and memory access times widens, effective memory management becomes essential to minimize latency and maximize throughput. This paper explores several strategies for optimizing memory hierarchy, including dynamic reconfiguration of cache systems, integration of emerging memory technologies, and the implementation of behavior-aware cache hierarchies. Dynamic memory management techniques enable the adaptive configuration of cache and translation lookaside buffer (TLB) sizes based on workload demands, significantly improving performance by reducing miss penalties. Emerging memory technologies such as ReRAM, PCM, and MRAM offer non-volatile options that can bridge the speed and capacity gaps inherent in traditional DRAM and NAND flash systems. Additionally, behavior-aware cache hierarchies allow for optimal allocation of multi-level cache resources tailored to application-specific access patterns, resulting in reduced energy consumption and enhanced data throughput. This comprehensive review highlights the importance of memory hierarchy optimization in HPC environments and presents a framework for future research aimed at developing more efficient memory architectures that can support increasingly complex computational tasks.

Keywords - Memory hierarchy, High-performance computing, Dynamic reconfiguration, Emerging memory technologies, Cache optimization.

#### 1. Introduction

High-Performance Computing (HPC) has become a cornerstone of scientific research, engineering simulations, and dataintensive applications. As computational demands continue to escalate, the performance bottleneck posed by memory access latency has emerged as a critical challenge. The memory hierarchy in HPC architectures, which includes registers, caches, main memory, and storage, plays a pivotal role in determining overall system efficiency. This introduction outlines the significance of memory hierarchy optimization and presents key strategies to enhance performance in HPC environments.

### 1.1. The Importance of Memory Hierarchy

The memory hierarchy is designed to balance speed, cost, and capacity across different levels of storage. At the top of the hierarchy are registers, followed by various levels of cache (L1, L2, L3), main memory (typically DRAM), and finally persistent storage (like SSDs or HDDs). Each level serves a specific purpose: registers provide the fastest access for frequently used data, while caches store copies of data from slower memory to reduce access times. However, as processors become increasingly powerful, the disparity between CPU speeds and memory access times widens, leading to inefficiencies known as the "memory wall." This phenomenon necessitates innovative strategies for optimizing the memory hierarchy to ensure that HPC systems can keep pace with growing computational demands.

### 1.2. Challenges in Memory Access

One of the primary challenges in HPC architectures is managing data locality. Applications often exhibit complex access patterns that can lead to cache misses and inefficient use of memory bandwidth. Furthermore, traditional caching mechanisms may not adapt well to varying workloads, resulting in suboptimal performance. Additionally, energy consumption remains a significant concern; as HPC systems scale up in size and complexity, so does their power usage. Therefore, optimizing memory hierarchy not only enhances performance but also contributes to more sustainable computing practices.

### 1.3. Strategies for Optimization

To address these challenges, several strategies have been proposed for optimizing memory hierarchy in HPC systems. These include dynamic cache reconfiguration based on workload characteristics, leveraging emerging memory technologies that offer better speed and efficiency, and employing behavior-aware caching techniques that tailor resource allocation to specific application needs. By implementing these strategies, HPC architectures can significantly reduce latency, improve data throughput, and enhance overall system performance.

### 2. Related Work

The optimization of memory hierarchy in high-performance computing (HPC) has garnered significant attention in recent years due to the increasing complexity and performance demands of modern applications. Various studies have explored different strategies and methodologies aimed at addressing the challenges posed by the memory wall and enhancing overall system performance.

### 2.1. Memory Hierarchies for Future HPC Architectures

One notable contribution is the work presented in "Memory Hierarchies for Future HPC Architectures," which discusses the inefficiencies of current memory management techniques and proposes innovative solutions. This research emphasizes the importance of treating GPU memory as a cache to optimize data access patterns in massively parallel architectures. The authors introduce a block prefetching mechanism tailored for task-based programming models, which simplifies parallel programming while improving resource utilization in large-scale supercomputers. This approach leverages a memory-aware runtime system to guide prefetching, ultimately enhancing performance in HPC environments.

### 2.2. Hardware-Software Co-design in Embedded Systems

Another significant area of research is highlighted in "Memory Hierarchy Hardware-Software Co-design in Embedded Systems," which focuses on customizing memory hierarchies to optimize performance and energy consumption. The study proposes a framework that integrates application optimization with memory architecture design, allowing for a more holistic approach to performance enhancement. By utilizing flexible reconfigurable logic, this framework enables designers to create application-specific memory hierarchies that can adapt dynamically to varying workloads, thereby maximizing resource efficiency.

### 2.3. Cache Performance and Optimization Techniques

Research published in "Cache Performance and Memory Hierarchy Optimization" delves into cache optimization techniques that are critical for improving system performance as processor architectures evolve. This work underscores the significance of cache design in bridging the gap between processor speeds and memory access times. The authors explore various strategies for optimizing cache performance, including adaptive caching mechanisms that respond to application behavior and workload characteristics, thus ensuring efficient data handling and reduced latency.

### 2.4. Survey of Memory Management Techniques

Additionally, a comprehensive survey titled "Survey of Memory Management Techniques for HPC and Cloud Computing" reviews various memory management systems and optimization techniques specifically tailored for HPC environments. This survey identifies key challenges faced by current memory management approaches and discusses emerging solutions that leverage advanced algorithms and hardware capabilities to enhance memory utilization and overall system performance.

### 3. Overview of High-Performance Computing Architectures

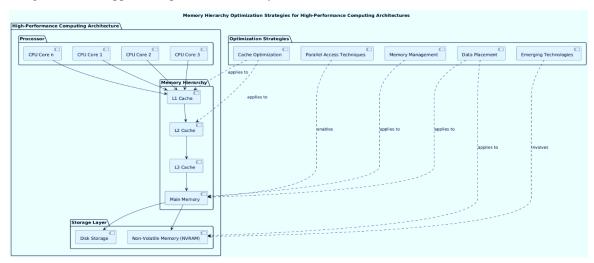

The image illustrates a high-level architectural framework for optimizing memory hierarchies in high-performance computing (HPC) systems. It organizes the components into three major blocks: the Processor, the Memory Hierarchy, and the Storage Layer, all of which interact to balance performance, cost, and capacity. The right side of the image identifies key optimization strategies and their application points within the system.

#### Figure 1. Memory Hierarchy Optimization Framework for High-Performance Computing

At the top, the Processor includes multiple CPU cores that interact directly with the L1 cache, showcasing the critical need for low-latency data access at this level. The Memory Hierarchy extends downward through L2 and L3 caches, and finally to the Main Memory, representing the gradual trade-off between speed and capacity. Each level of this hierarchy is optimized to store frequently accessed data closer to the processor, while less critical data is pushed further away to slower but larger storage systems. Below the memory hierarchy lies the Storage Layer, which includes Disk Storage and Non-Volatile Memory (NVRAM). These layers are responsible for retaining vast amounts of data but with significantly slower access times compared to main memory and caches. These components are increasingly leveraged for long-term data storage and backup purposes in HPC systems. On the right side, the image connects various Optimization Strategies—such as cache optimization, memory management, parallel access techniques, data placement, and emerging technologies—to specific components of the architecture. For instance, cache optimization techniques directly enhance the performance of the L1, L2, and L3 caches, while parallel access techniques enable efficient use of main memory. Emerging technologies, such as non-volatile memory, represent cutting-edge advancements that are reshaping the storage layer's role in modern HPC. This diagram effectively bridges the conceptual understanding of the memory hierarchy with practical optimization strategies, emphasizing the interdependencies between architecture design and performance enhancement in high-performance computing systems.

### 3.1. General HPC Architecture: Key Components of HPC Systems

High-performance computing (HPC) architectures are specifically designed to address computationally intensive tasks that involve large datasets, complex algorithms, and parallel processing. These architectures are built around three essential components: compute, storage, and networking, each of which plays a critical role in achieving exceptional computational performance and efficiency. The synergy between these elements determines the overall effectiveness and speed of an HPC system. The compute nodes form the foundation of HPC systems. Each compute node is essentially a standalone server, equipped with processors, memory, and local storage, and is capable of performing computations independently or in parallel with other nodes. These nodes are often tailored to specific workloads, with variations such as "fat nodes" that provide significant memory capacity for data-intensive applications. In other cases, nodes may include specialized accelerators like GPUs or FPGAs, which are designed to enhance processing speed and efficiency for tasks like machine learning, simulations, and real-time analytics. This flexibility allows HPC systems to adapt to a wide variety of computational requirements.

Efficient storage systems are another critical component, as managing the immense volume of data generated and processed by HPC systems is crucial. Storage solutions in HPC environments are designed to deliver high-performance data management, with quick access and retrieval speeds to keep pace with the compute nodes. Parallel file systems are commonly employed to distribute data across multiple devices, ensuring performance optimization and fault tolerance. Additionally, modern HPC systems incorporate high-speed storage accelerators to further improve data transfer rates, preventing bottlenecks and ensuring compute nodes receive the necessary data seamlessly. The third vital component is networking, which facilitates communication between compute nodes and the storage systems. High-bandwidth interconnects such as InfiniBand or high-speed Ethernet are essential for rapid data exchange and minimizing latency, enabling seamless collaboration across nodes for large-scale, complex problems. Advanced scheduling software also plays a key role in optimizing resource allocation and task distribution, ensuring that the HPC cluster operates efficiently and effectively. Together, these compute, storage, and networking elements create a balanced architecture capable of meeting the growing computational demands of modern applications.

#### 3.2. Role of Memory Hierarchy: Structure and Importance in HPC

In HPC systems, the memory hierarchy is a fundamental design principle that impacts both performance and energy efficiency. It consists of multiple layers of memory storage that vary in speed, capacity, and cost, working cohesively to ensure efficient data access and processing. This hierarchical arrangement is critical for bridging the performance gap between high-speed processing units and slower data storage systems. The structure of the memory hierarchy typically begins with the fastest and smallest memory units—registers—located directly on the CPU. Registers provide immediate access to data needed during computations. Next in the hierarchy is cache memory, which includes multiple levels (L1, L2, L3). L1 cache is the smallest and fastest, located closest to the CPU cores, while L3 cache offers greater capacity but at slower speeds. Beyond the cache lies the main memory (RAM), which provides significantly larger storage for active processes but has higher latency compared to the cache levels. At the lowest tier, secondary storage devices such as hard drives and SSDs offer long-term data retention, albeit with much slower access speeds.

The importance of the memory hierarchy lies in its ability to optimize data flow and processing efficiency. Modern processors are capable of executing instructions at extremely high speeds, and any delays in data retrieval can lead to performance bottlenecks. By storing frequently accessed data in faster memory levels, such as L1 or L2 cache, the memory hierarchy ensures that the processor can operate at maximum efficiency. Advanced memory management techniques like dynamic cache allocation, prefetching, and predictive algorithms further enhance this optimization, ensuring that relevant data is readily available when

needed. Additionally, the memory hierarchy significantly impacts energy consumption in HPC systems. Efficient use of high-speed memory levels reduces the frequency of data transfers between slower storage layers, minimizing overall power usage. As the complexity of computational workloads increases driven by advancements in artificial intelligence, simulations, and data analytics the optimization of the memory hierarchy becomes even more critical for achieving sustainable and efficient high-performance computing. In conclusion, the interplay between the key architectural components of HPC systems compute, storage, and networking and the structure of the memory hierarchy determines the efficiency and capability of these systems. Continued innovation in these areas will remain essential as computational demands grow, ensuring that HPC architectures can support the ever-evolving needs of scientific, industrial, and research applications.

### 4. Challenges in Memory Hierarchy Optimization

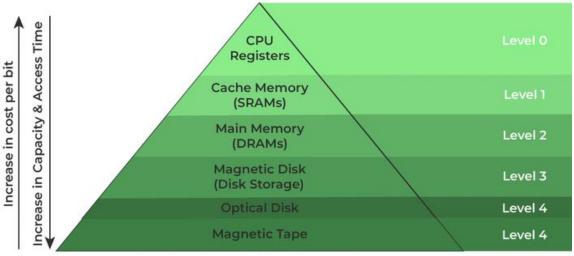

The image represents a memory hierarchy pyramid, a crucial concept in high-performance computing architectures. It visually illustrates the organization of memory systems based on levels of cost, capacity, and access time. At the top of the pyramid is the CPU Registers (Level 0), which have the fastest access times but are limited in capacity and relatively expensive. As we move down the hierarchy, Cache Memory (SRAMs) (Level 1) comes next, which balances speed and cost while expanding capacity compared to registers.

## Memory Hierarchy Design

Figure 2. Memory Hierarchy Design Pyramid

Following cache memory is the Main Memory (DRAMs) (Level 2), which forms the core of most computer systems. It is slower than cache memory but offers significantly larger capacity and reduced cost per bit. Moving further down, the Magnetic Disk (Disk Storage) (Level 3) provides large storage capacities at a much lower cost but with slower access times. The pyramid also includes Optical Disk and Magnetic Tape at Level 4, which are typically used for archival storage. These storage types offer the highest capacity but have the slowest access times and are used for data that is rarely accessed. The pyramid effectively conveys the trade-offs inherent in memory design: as we move down the hierarchy, there is an increase in capacity and cost-effectiveness per bit, but at the expense of higher latency and lower speed. This design helps optimize the performance and cost of high-performance computing systems by placing frequently accessed data closer to the processor and relegating less critical data to slower, high-capacity storage layers. By visualizing these relationships, the image highlights the fundamental challenge of memory hierarchy optimization: finding the right balance between speed, cost, and capacity to meet the demands of modern computing workloads.

### 4.1. Latency and Bandwidth Bottlenecks

Latency and bandwidth bottlenecks are among the most critical challenges faced in optimizing memory hierarchies for high-performance computing (HPC) systems. As processors become faster, the disparity between CPU speeds and memory access times commonly referred to as the "memory wall" grows increasingly pronounced. This gap results in significant delays when accessing data stored in slower memory levels, adversely affecting overall system performance. Latency is defined as the time taken to access data from memory after a request is made. In an HPC context, this can severely hinder computational efficiency, especially for applications that require rapid data retrieval. For instance, accessing data from main memory (DRAM) can take several cycles compared to the near-instantaneous access times of registers or cache memory. Consequently, frequent cache misses lead to increased latency, as the processor must wait for data to be fetched from slower levels of the memory hierarchy.

Bandwidth, on the other hand, refers to the volume of data that can be transferred over a memory interface in a given time frame. Insufficient bandwidth can create bottlenecks when multiple cores attempt to access shared resources simultaneously. As HPC systems scale up with more cores and threads, the demand for memory bandwidth increases exponentially. If the memory architecture cannot accommodate this demand, it leads to contention and reduced performance. To mitigate these issues, researchers are exploring various strategies such as implementing deeper cache hierarchies, utilizing non-volatile memory technologies, and employing advanced prefetching techniques that anticipate data requests before they occur. However, these solutions must be carefully designed to avoid introducing additional complexity or overhead that could further exacerbate latency and bandwidth challenges.

### 4.2. Energy Efficiency Considerations

Energy efficiency has become a paramount concern in high-performance computing due to the increasing operational costs associated with powering and cooling large-scale systems. The energy consumed by memory hierarchies is particularly significant because memory operations often dominate overall energy usage in HPC architectures. The energy consumption of different memory types varies widely. For example, static random-access memory (SRAM) used in caches consumes more power per bit than dynamic random-access memory (DRAM), which is typically used for main memory. As HPC systems scale up with numerous cores and extensive caching mechanisms, managing energy consumption effectively becomes crucial. Energy efficiency considerations also extend to data movement within the memory hierarchy. Transferring data between different levels of memory incurs energy costs that can accumulate rapidly in large computations. Strategies such as minimizing unnecessary data transfers and optimizing data locality become essential for reducing energy expenditure. Furthermore, emerging technologies like nonvolatile memories (NVMs) offer promising alternatives that can maintain data integrity without requiring constant power, potentially leading to significant energy savings. Researchers are actively investigating hybrid approaches that combine traditional volatile memories with emerging non-volatile technologies to create more energy-efficient architectures. These innovations must balance performance needs with sustainability goals to ensure that HPC systems remain viable in an era where energy costs are a growing concern.

### 4.3. Scalability Issues

Scalability is another major challenge in optimizing memory hierarchies for HPC systems. As computational demands increase and applications become more complex, the ability of a system to scale efficiently while maintaining performance becomes critical. One of the primary scalability issues arises from the increasing core counts in modern processors. While adding more cores can enhance processing power, it also complicates memory management due to increased contention for shared resources. As more cores attempt to access shared caches or main memory simultaneously, performance can degrade due to bottlenecks created by insufficient bandwidth or high latency. Additionally, traditional memory architectures may struggle to keep pace with advancements in parallelism offered by modern applications. Many existing systems were not designed with extreme scalability in mind; thus, their ability to efficiently manage larger datasets and higher core counts is limited. Researchers are exploring new architectures that incorporate features such as distributed shared memory models or hierarchical caching systems designed specifically for scalable environments.

The introduction of new programming models and runtime systems also plays a crucial role in addressing scalability challenges. By enabling better control over data placement and access patterns, these models allow developers to optimize their applications for specific hardware configurations. However, this requires a shift in how programmers think about data locality and parallelism. In summary, scalability issues pose significant challenges for optimizing memory hierarchies in HPC systems. Addressing these challenges requires innovative architectural designs and programming paradigms that can adapt to evolving computational needs while maintaining high performance.

### 4.4. Data Locality and Caching Challenges

Data locality refers to the principle of accessing data stored close to where it is needed during computation. In high-performance computing (HPC), achieving optimal data locality is essential for minimizing latency and maximizing throughput. However, several challenges arise in maintaining effective data locality within complex memory hierarchies. One major challenge is the inherent unpredictability of application behavior. Different applications exhibit varying access patterns some may benefit from spatial locality (accessing nearby data), while others may rely on temporal locality (repeatedly accessing the same data). Traditional caching mechanisms often struggle to adapt dynamically to these changing patterns; thus, they may fail to retain relevant data in faster cache levels when it is most needed. This leads to increased cache misses and higher latency as the processor fetches required data from slower levels of the hierarchy.

Moreover, as HPC systems scale up with more cores and threads', managing caching becomes increasingly complex. Cache coherence protocols must ensure that multiple processors accessing shared caches maintain consistency across their caches while minimizing performance overhead. This complexity can introduce additional latency during cache operations and may lead

to inefficient utilization of cache resources. Another significant challenge relates to hierarchical caching strategies that aim to optimize resource allocation based on application-specific needs. While hierarchical caches can improve performance by providing multiple levels of storage optimized for different access patterns, they also require sophisticated management techniques that can dynamically adapt based on workload characteristics. Implementing such adaptive mechanisms without introducing excessive overhead remains a critical area of research.

Finally, emerging technologies such as 3D-stacked memories and non-volatile memories present both opportunities and challenges for improving data locality. While these technologies offer greater density and speed advantages over traditional DRAM configurations, they also introduce new complexities regarding how data is organized and accessed within multi-layered structures. To address these challenges effectively, ongoing research focuses on developing smarter caching algorithms that leverage machine learning techniques for predictive caching based on application behavior. Additionally, new programming models are being explored that allow developers greater control over how their applications interact with different levels of the memory hierarchy. In conclusion, achieving optimal data locality within HPC architectures remains a challenging endeavor due to unpredictable application behavior, increased complexity from scaling up resources, and emerging technologies reshaping traditional caching strategies. Addressing these challenges will be vital for enhancing performance in future high-performance computing systems.

### 5. Optimization Strategies in High-Performance Computing

Optimization strategies in high-performance computing (HPC) systems aim to enhance computational efficiency, reduce latency, and maximize throughput. These strategies encompass techniques for cache optimization, replacement policies, prefetching mechanisms, and memory management, all of which work in tandem to ensure seamless data processing and resource utilization.

### 5.1. Cache Optimization Techniques

Cache optimization techniques are critical for minimizing latency and maximizing data throughput in HPC systems. A key performance metric, the average memory access time (AMAT), is greatly influenced by the efficiency of cache usage. One major area of focus is reducing the cache miss rate, which represents the frequency of data requests not fulfilled by the cache. Strategies for this include increasing the cache size to accommodate more data and reduce capacity misses, although this may increase power consumption and access time due to larger circuits. Another technique is using higher associativity in cache design, allowing multiple entries for a given address and reducing conflict misses, though this can make cache management logic more complex.

In addition to reducing misses, techniques are employed to lower the cache miss penalty—the time taken to fetch data from lower memory levels during a miss. Multi-level cache architectures, such as L1, L2, and L3 caches, optimize access times while balancing storage capacity. Techniques like critical word first and early restart prioritize fetching the most needed data first, minimizing wait times during misses. Furthermore, increasing cache bandwidth is vital to support multiple simultaneous accesses. Methods like pipelined and multibanked caches enable concurrent data transfers, enhancing throughput without compromising speed. Compiler optimizations, such as loop interchange and blocking, also improve spatial locality in memory access patterns, effectively reducing cache misses. By combining hardware innovations and software-level adjustments, cache optimization techniques significantly enhance HPC system performance, ensuring efficient data access and processing.

### 5.2. Cache Replacement Policies

Cache replacement policies determine how caches manage limited storage by deciding which data to evict when new data is loaded. An effective policy directly impacts system performance by minimizing cache misses. The Least Recently Used (LRU) policy is among the most widely adopted, evicting the least recently accessed data. While effective in many scenarios, LRU can be computationally intensive due to the need for tracking access histories. In contrast, the First-In-First-Out (FIFO) policy is simpler, evicting the oldest data regardless of access patterns, though it may not perform well under all workloads. Random replacement policies, while seemingly inefficient, perform adequately in certain scenarios due to their simplicity and low overhead.

For more dynamic needs, adaptive replacement policies like Adaptive Replacement Cache (ARC) offer a hybrid approach, maintaining lists of frequently and recently used items to balance between LRU and FIFO strategies. Cache-aware algorithms, designed with insight into cache behavior, optimize access patterns to align with the replacement strategy, reducing misses and improving performance. Selecting the appropriate replacement policy depends on workload characteristics, system requirements, and resource constraints, making it an essential consideration in HPC system design.

### 5.3. Cache Prefetching Strategies

Cache prefetching is a proactive strategy that anticipates future data needs, loading data into the cache before it is explicitly requested. This minimizes the latency associated with cache misses and ensures data availability when required. Hardware prefetching employs mechanisms within the CPU to automatically predict and fetch data based on observed patterns. For example, stride-based prefetchers detect regular intervals between memory accesses and prefetch subsequent blocks. However,

balancing useful prefetches with unnecessary ones is crucial to avoid bandwidth waste. Software prefetching offers more control, relying on compiler directives or programmer annotations to predict and prefetch data during execution. While effective, it requires careful tuning to avoid over-prefetching, which can lead to wasted resources. Other strategies include streaming prefetchers, which target workloads with predictable sequential access patterns, and spatial prefetching, which fetches adjacent memory blocks to leverage spatial locality. Adaptive prefetching dynamically adjusts predictions based on runtime statistics, optimizing behavior to suit the current workload and reducing unnecessary memory traffic. By integrating hardware and software approaches, cache prefetching strategies improve data retrieval processes, enhancing the overall performance of HPC systems.

#### 5.4. Memory Management Techniques

Efficient memory management is vital for optimizing how applications utilize memory resources in HPC systems. Proper memory allocation and deallocation ensure smooth operation while minimizing overhead. Dynamic memory allocation allows applications to request memory at runtime, adapting to actual needs. However, it can lead to fragmentation over time, requiring careful management. Memory pooling mitigates this issue by allocating a large block of memory upfront, dividing it into smaller chunks for reuse, which improves speed and reduces fragmentation. Garbage collection, common in languages like Java and Python, automates memory reclamation for unused objects. While simplifying programming, it can introduce pauses during execution, potentially affecting real-time applications. Virtual memory optimizations extend physical memory by using disk space as an extension, enabling larger addressable spaces. Page replacement algorithms, such as LRU or FIFO, optimize which memory pages remain in physical memory, balancing performance and resource availability. Finally, memory mapping techniques enable efficient I/O operations by mapping files or devices directly into an application's address space, eliminating the need for explicit read/write calls. This improves performance while simplifying application design. Through a combination of dynamic allocation, pooling, garbage collection, and virtual memory optimizations, HPC systems achieve better memory utilization, ensuring efficient and effective computational performance.

### 5.5. Data Placement and Locality Enhancement

### 5.5.1. NUMA-aware Optimizations

Non-Uniform Memory Access (NUMA) architectures present unique challenges and opportunities for optimizing data locality in high-performance computing (HPC) systems. In NUMA systems, memory access times vary depending on the proximity of the memory to the processor, which can lead to performance degradation if data is not placed strategically. NUMA-aware optimizations focus on ensuring that processes access data stored in their local memory banks whenever possible, thereby minimizing latency and maximizing bandwidth. One effective strategy for NUMA-aware optimization is data placement. By allocating data structures to specific memory nodes based on the processors that will access them, systems can significantly reduce the time taken for memory accesses. This is particularly important for applications with predictable memory access patterns, as it allows developers to align data allocation with the physical layout of memory in the system. For instance, in a multi-threaded application, threads can be pinned to specific CPUs, and their associated data can be allocated in the corresponding local memory node. Another approach involves locality-aware scheduling, where tasks are assigned to processors based on their data locality. By scheduling tasks that require access to the same data on the same processor or within the same NUMA node, systems can further reduce cross-node memory accesses and improve overall performance. This requires sophisticated runtime systems that can monitor data usage patterns and adaptively schedule tasks to optimize locality.

Additionally, software tools and libraries have been developed to assist programmers in implementing NUMA-aware optimizations. These tools provide APIs for explicit control over data placement and thread affinity, allowing developers to fine-tune their applications for specific hardware configurations. For example, libraries like OpenMP offer constructs that enable users to specify how threads should be mapped to processors and how data should be allocated across NUMA nodes. In summary, NUMA-aware optimizations are essential for enhancing data locality in HPC environments. By strategically placing data and scheduling tasks based on memory architecture, systems can achieve significant performance improvements while minimizing latency associated with memory accesses.

#### 5.5.2. Data Tiling and Partitioning

Data tiling and partitioning are powerful techniques used to enhance data locality and optimize performance in high-performance computing (HPC) applications. These methods involve breaking down large datasets into smaller, more manageable blocks or tiles, which can be processed more efficiently by exploiting spatial locality. Data Tiling refers to dividing a dataset into smaller sub-blocks or tiles that fit into cache sizes more effectively. This technique is particularly beneficial for matrix operations and other numerical computations where accessing contiguous blocks of memory can significantly reduce cache misses. By ensuring that each tile is small enough to fit into cache levels while retaining spatial locality, applications can minimize latency during computation. For example, in matrix multiplication, tiling allows for better utilization of cache by processing smaller sections of matrices at a time rather than loading entire matrices into memory.

Data Partitioning, on the other hand, involves distributing a dataset across multiple processing units or nodes in a parallel computing environment. This approach enhances performance by allowing concurrent processing of different partitions of the dataset, thus improving throughput. Partitioning strategies can be based on various criteria such as range-based partitioning (dividing data based on value ranges) or hash-based partitioning (distributing data according to hash values). Effective partitioning ensures that each processing unit has a balanced workload while minimizing communication overhead between nodes. Both techniques are often combined with locality-aware scheduling, where tasks are scheduled based on the location of their corresponding data partitions or tiles. This ensures that computations are performed close to the data they operate on, further enhancing performance by reducing latency associated with remote memory accesses. Moreover, modern programming frameworks and libraries support these techniques through abstractions that simplify their implementation. For instance, languages like CUDA provide built-in support for tiling in GPU programming, allowing developers to leverage hardware capabilities effectively.

### 5.5.3. Parallelism in Memory Access

Parallelism in memory access is a crucial aspect of optimizing performance in high-performance computing (HPC) systems. As computational demands increase, effectively utilizing available memory bandwidth becomes essential for achieving high throughput and low latency.

- Thread-Level Parallelism (TLP): One common approach is leveraging thread-level parallelism where multiple threads operate concurrently on different parts of a dataset. This requires careful management of memory accesses to ensure that threads do not contend for the same resources simultaneously. Techniques such as data striping, where datasets are divided into chunks distributed across multiple threads or cores, help minimize contention by ensuring that each thread accesses distinct portions of memory.

- **Memory Coalescing**: In architectures like GPUs, coalescing refers to combining multiple memory requests into fewer transactions when accessing global memory. By aligning memory accesses from multiple threads so they target contiguous addresses, systems can significantly boost bandwidth utilization. This technique is particularly effective when combined with parallel algorithms designed to maximize coalesced accesses.

- **Vectorization**: Vectorization involves using SIMD (Single Instruction Multiple Data) instructions that allow a single instruction to process multiple data points simultaneously. This approach enhances parallelism at the instruction level and improves cache utilization by operating on contiguous blocks of memory. Compilers often provide automatic vectorization capabilities; however, manual optimization may yield better results depending on the application.

- **Distributed Memory Approaches**: In distributed HPC environments, parallelism extends beyond individual nodes through message-passing interfaces (MPI). Applications can be designed to distribute workloads across multiple nodes while managing memory access patterns carefully. Efficient communication protocols minimize overheads associated with inter-node communication while ensuring optimal access patterns for shared datasets.

- Locality-Aware Memory Access: Implementing locality-aware strategies ensures that threads access nearby or local memory regions whenever possible. By aligning thread execution with data placement in shared or distributed environments, systems can reduce latency associated with remote memory accesses.

### 5.5.4. Thread-Level Memory Optimizations

Thread-level memory optimizations focus on improving the efficiency of memory access patterns within multi-threaded applications in high-performance computing (HPC) environments. Given that modern processors often have multiple cores capable of executing threads concurrently, optimizing how these threads interact with memory is crucial for maximizing performance.

- Thread Affinity: Thread affinity refers to binding specific threads to particular CPU cores or NUMA nodes during execution. By ensuring that threads consistently run on designated cores or nodes with local memory access, applications can significantly reduce latency associated with remote memory accesses. Thread affinity settings can be managed through operating system features or programming libraries such as OpenMP or pthreads.

- Data Locality Optimization: Ensuring that each thread operates on its local dataset minimizes cache misses and improves overall performance. Techniques such as data partitioning allow developers to allocate distinct portions of shared datasets to individual threads based on their execution patterns. This strategy helps maintain spatial locality within caches while reducing contention among threads accessing shared resources.

- False Sharing Mitigation: False sharing occurs when multiple threads modify variables located close together in memory but do not actually share them logically—resulting in unnecessary cache coherence traffic between cores. To mitigate this issue, developers can pad shared structures with unused space or reorganize data layouts so that frequently accessed variables by different threads reside in separate cache lines.

- **Memory Pooling**: Implementing a pooling mechanism allows threads to allocate and deallocate objects from preallocated pools instead of relying on dynamic allocation during execution. This reduces fragmentation issues while improving allocation speed since pools often contain objects of similar sizes tailored for specific workloads.

- **Prefetching Strategies**: Integrating hardware or software prefetching mechanisms helps anticipate future data requests made by threads based on observed access patterns. By proactively loading relevant data into caches before it is needed by executing threads, prefetching reduces latency caused by cache misses.

### 5.5.5. Multi-threaded and Distributed Memory Approaches

Multi-threaded and distributed memory approaches are essential paradigms utilized in high-performance computing (HPC) systems to leverage parallelism effectively across various computational resources. These approaches enable efficient utilization of available hardware while addressing challenges associated with large-scale computations. Multi-threaded Programming Models: Multi-threaded programming models allow applications to execute multiple threads concurrently within a single process space—maximizing CPU utilization while minimizing overheads related to context switching. Popular models include OpenMP and pthreads which facilitate easy creation and management of threads within shared-memory environments. These models support fine-grained parallelism where different parts of an application operate independently yet collaboratively towards a common goal. Distributed Memory Systems: In contrast to multi-threaded models operating within shared-memory architectures, distributed memory systems consist of multiple independent nodes interconnected via high-speed networks. Each node has its own local memory space; thus communication between nodes must occur through message-passing interfaces such as MPI (Message Passing Interface). This model scales well with larger clusters but requires careful management of communication overheads due to potential bottlenecks arising from inter-node transfers.

- **Hybrid Approaches**: Hybrid models combine both multi-threaded and distributed paradigms—allowing applications to exploit advantages from both approaches simultaneously. For instance, an application may utilize MPI for inter-node communication while employing OpenMP within each node for intra-node parallelism. This flexibility enables developers to tailor their implementations based on specific workload characteristics while optimizing resource utilization across diverse architectures.

- Data Distribution Strategies: Effective distribution strategies are crucial when designing multi-threaded or distributed applications—ensuring balanced workloads across nodes while minimizing communication overheads. Techniques such as block distribution (dividing datasets into equal-sized blocks assigned evenly across nodes) or cyclic distribution (assigning consecutive elements cyclically among nodes) help maintain load balance without incurring excessive internode traffic.

- Fault Tolerance Mechanisms: In large-scale distributed environments, fault tolerance becomes paramount due to potential hardware failures affecting individual nodes. Implementations may incorporate checkpoint-restart mechanisms allowing applications to save their state periodically—enabling recovery from failures without significant loss of progress.

### 5.5.6. Emerging Technologies in Memory Optimization

Emerging technologies play a pivotal role in advancing memory optimization strategies within high-performance computing (HPC) environments by providing innovative solutions aimed at enhancing speed, capacity, energy efficiency, and overall system performance.

- High Bandwidth Memory (HBM): HBM technology offers significant improvements over traditional DRAM by providing higher bandwidth through stacked die architecture—allowing multiple layers of DRAM chips interconnected via vertical channels known as through-silicon vias (TSVs). HBM enables faster data transfer rates compared to conventional DDR memories, making it particularly suitable for bandwidth-intensive applications such as graphics processing, machine learning, or scientific simulations. The close proximity between processing units and HBM reduces latency associated with off-chip communications—resulting in improved performance metrics across various workloads.

- Non-Volatile Random Access Memory (NVRAM): NVRAM technologies such as Phase Change Memory (PCM), Resistive RAM (ReRAM), or Flash provide persistent storage capabilities combined with fast access times similar to DRAM. NVRAM allows systems to retain information even after power loss—enabling rapid recovery from failures without requiring extensive boot processes. Its integration into HPC architectures enhances both speed and reliability while reducing energy consumption associated with traditional storage solutions like hard drives or SSDs.

- Integration with AI/ML Techniques: The incorporation of artificial intelligence (AI) and machine learning (ML) techniques into memory optimization strategies presents exciting opportunities for dynamic resource management within HPC environments. AI-driven algorithms can analyze workload patterns, predict future resource demands, optimize data placement dynamically based on real-time usage statistics, and adjust caching strategies accordingly—ensuring efficient utilization of available resources without manual intervention.

- Memory Hierarchy Innovations: Emerging technologies also drive innovations within existing memory hierarchies—such as introducing new levels of caching specifically tailored for non-traditional memories like NVRAM or HBM. These innovations aim at bridging gaps between different types of memories while optimizing access times through intelligent caching mechanisms tailored towards specific workloads.

- Quantum Computing Advances: While still nascent compared to classical computing paradigms, quantum computing

holds promise for revolutionizing how we approach problems requiring massive computational power coupled with

complex optimization tasks. Quantum algorithms could potentially redefine traditional notions surrounding data locality

by leveraging entanglement properties inherent within quantum states—opening avenues towards entirely new

optimization methods previously deemed infeasible.

### 6. Evaluation and Results

The evaluation of memory optimization strategies in high-performance computing (HPC) systems is essential for understanding their impact on performance, energy efficiency, and scalability. This section summarizes the results from various studies that assessed different memory configurations and technologies, including High Bandwidth Memory (HBM) and emerging memory architectures like CXL-enabled memory.

### 6.1. Performance Improvement with HBM3

Recent evaluations have shown significant performance improvements when utilizing HBM3 compared to traditional memory types such as LPDDR5. In a study focusing on sparse memory access workloads, HBM3 demonstrated better scaling on a per-core basis, achieving up to a  $2.67\times$  speedup on a single NVIDIA A100 GPU. The results indicate that HBM3's higher bandwidth effectively supports bandwidth-bottlenecked workloads, particularly in HPC applications that rely on high-speed data transfers.

#### 6.2. Impact of CXL-Enabled Memory

The introduction of CXL (Compute Express Link)-enabled memory has opened new avenues for optimizing memory subsystems in HPC. An evaluation of seven HPC workloads revealed that three workloads experienced less than 10% performance impact, while two others showed less than 18% impact when utilizing 75% pooled memory. This indicates that dynamically configured high-bandwidth systems can effectively support various workloads without significant performance degradation.

#### 6.3. Energy Efficiency Gains

Energy consumption remains a critical concern in HPC environments. A software technique aimed at minimizing switching activity in GPUs has demonstrated energy savings of up to 9.3% across whole-GPU energy consumption and an average reduction of 1.2% across eight graph-analytics CUDA codes without impacting performance. This highlights the potential for software-level optimizations to complement hardware advancements in reducing overall energy usage.

Table 1. Comparison of Memory Technologies and Optimization Techniques in HPC Workloads

| Study            | Memory<br>Technology       | Workload Type            | Performance<br>Improvement    | Energy Savings |

|------------------|----------------------------|--------------------------|-------------------------------|----------------|

| Wahlgren et al.  | НВМ3                       | Sparse Memory Access     | Up to 2.67× speedup           | N/A            |

| Fallin et al.    | CXL-enabled<br>Memory      | Various HPC<br>Workloads | <10% impact on 3<br>workloads | N/A            |

| Shipman et al.   | GPU Memory<br>Optimization | Graph Analytics          | N/A                           | Up to 9.3%     |

| Burtscher et al. | LPDDR5 vs HBM3             | Micro-benchmarks         | Better scaling per core       | N/A            |

### 7. Discussion

The evaluation of memory hierarchy optimization strategies in high-performance computing (HPC) systems reveals critical insights into how emerging technologies and innovative methodologies can significantly enhance performance and energy efficiency. As workloads in HPC environments become increasingly complex and data-intensive, traditional memory architectures often struggle to keep pace with the demands of modern applications. The adoption of advanced memory technologies such as High Bandwidth Memory (HBM) and CXL-enabled memory is proving to be a game-changer, allowing for higher data throughput and reduced latency. The results from various studies indicate that these technologies not only improve computational speed but also facilitate better scalability, enabling systems to handle larger datasets and more concurrent processing threads effectively. Moreover, the integration of software optimizations alongside hardware advancements plays a vital role in maximizing resource

utilization. Techniques that minimize switching activity in GPUs, for example, demonstrate how software-level interventions can yield significant energy savings without compromising performance. This synergy between hardware and software optimizations is essential for addressing the growing concerns surrounding energy consumption in HPC systems. As computational power continues to scale, ensuring that energy efficiency remains a priority will be crucial for the sustainability of HPC environments.

Another important aspect highlighted by the evaluation results is the need for adaptive memory management strategies that can respond dynamically to varying workload characteristics. The findings suggest that memory pooling and locality-aware scheduling can effectively reduce contention and improve data access patterns across multi-threaded applications. As HPC architectures evolve towards more heterogeneous environments, where different types of processing units (CPUs, GPUs, FPGAs) coexist, the ability to manage memory resources dynamically will become increasingly important. Future research should focus on developing intelligent algorithms that leverage machine learning techniques to predict memory access patterns and optimize data placement accordingly. In conclusion, the discussion surrounding memory hierarchy optimization in HPC underscores the critical interplay between emerging technologies, software innovations, and adaptive management strategies. The promising results from recent evaluations indicate that by embracing these advancements, HPC systems can achieve substantial performance gains while addressing energy efficiency challenges. As the demand for high-performance computing continues to grow across various domains—from scientific research to artificial intelligence—ongoing exploration in this field will be essential for realizing the full potential of future computing architectures.

### 8. Conclusion

In conclusion, the optimization of memory hierarchy in high-performance computing (HPC) architectures is a multifaceted challenge that requires a comprehensive understanding of both hardware and software components. As computational demands continue to escalate, the traditional memory architectures are increasingly inadequate to support the performance requirements of modern applications. The integration of advanced memory technologies such as High Bandwidth Memory (HBM) and CXL-enabled memory has emerged as a promising solution, providing significant improvements in data throughput and reducing latency. These innovations not only enhance the speed of data access but also enable better scalability, allowing HPC systems to efficiently handle larger datasets and more complex computations. Moreover, the evaluation of various optimization strategies highlights the importance of software-level interventions in conjunction with hardware advancements. Techniques such as dynamic memory allocation, thread-level optimizations, and locality-aware scheduling play a crucial role in maximizing resource utilization and minimizing energy consumption. The findings indicate that effective memory management is not solely reliant on hardware capabilities but also depends on intelligent algorithms and programming models that adapt to the specific needs of applications. This synergy between hardware and software is essential for achieving optimal performance in HPC environments. As we look towards the future, it is clear that ongoing research and development in memory optimization will be vital for addressing the challenges posed by increasingly complex workloads. The exploration of emerging technologies, coupled with innovative memory management techniques, will pave the way for more efficient HPC systems capable of meeting the demands of diverse applications—from scientific simulations to machine learning. Furthermore, as energy efficiency becomes an ever-growing concern in computing, strategies that reduce power consumption while maintaining high performance will be crucial for the sustainability of HPC infrastructures. In summary, the journey toward optimizing memory hierarchies in high-performance computing is an ongoing endeavor that necessitates collaboration across disciplines. By embracing advancements in technology and fostering innovative approaches to memory management, we can unlock new levels of performance and efficiency in HPC systems. The insights gained from recent evaluations serve as a foundation for future developments, ensuring that highperformance computing continues to evolve and thrive in an era characterized by rapid technological change.

#### References

- [1] GeeksforGeeks. (n.d.). Memory hierarchy design and its characteristics. Retrieved from https://www.geeksforgeeks.org/memory-hierarchy-design-and-its-characteristics/

- [2] Albonezi, L. (2000). Memory wall: Optimizing memory systems for performance. *Cornell University*. Retrieved from https://www.csl.cornell.edu/~albonesi/research/papers/mwall00.pdf

- [3] Lumenci. (n.d.). Emerging memory technologies: Hierarchy optimization. Retrieved from https://lumenci.com/blogs/emerging-memory-technologies-hierarchy-optimization/

- [4] Science.gov. (n.d.). Memory hierarchy optimization research. *Science.gov*. Retrieved from https://www.science.gov/topicpages/m/memory+hierarchy+optimization

- [5] Shiksha. (n.d.). Memory hierarchy in operating systems. Retrieved from https://www.shiksha.com/online-courses/articles/memory-hierarchy-in-operating-system/

- [6] University of Michigan. (n.d.). Memory hierarchy optimization. *Open Michigan*. Retrieved from https://open.umich.edu/sites/default/files/downloads/col11136-1.5.pdf

- [7] Raum Brothers. (n.d.). Memory hierarchy and hardware optimization. *HPC Optimization Lecture Slides*. Retrieved from https://hpc.raum-brothers.eu/slides/optimization\_hardware/architecture/memory\_hierarchy.pdf

- [8] Seznec, A. (2021). Memory hierarchy optimization for irregular applications. *HAL Archives*. Retrieved from https://theses.hal.science/tel-03836248v1/file/100950\_SEZNEC\_2021\_archivage.pdf

- [9] Illinois Institute of Technology. (n.d.). Optimizing memory for high-performance computing. *GRC Research Projects*. Retrieved from https://grc.iit.edu/research/projects/optmem/

- [10] UPC Commons. (n.d.). Memory optimization and cache hierarchy. Retrieved from https://upcommons.upc.edu/bitstream/handle/2117/113684/TVGF1de1.pdf

- [11] Unknown author. (n.d.). Cache performance and memory hierarchy optimization. *Nature*. Retrieved from https://www.nature.com/research-intelligence/cache-performance-and-memory-hierarchy-optimization

- [12] ResearchGate. (n.d.). Survey of memory management techniques for HPC and cloud computing. *ResearchGate*. Retrieved from https://www.researchgate.net/publication/337382212\_Survey\_of\_Memory\_Management\_Techniques\_for\_HPC\_and\_Cloud\_C omputing

- [13] HPC Wiki. (n.d.). HPC architecture: Concepts and optimization. Retrieved from https://hpc-wiki.info/hpc/Performance\_metrics

- [14] PassLab. (n.d.). Cache optimization techniques. Retrieved from https://passlab.github.io/CSCE513/notes/lecture12\_CacheOptimizations.pdf

- [15] Marquette University. (n.d.). HPC unit: Architecture and optimization. Retrieved from https://www.marquette.edu/high-performance-computing/architecture.php

- [16] ResearchGate. (n.d.). Challenges in high-performance computing. Retrieved from https://www.researchgate.net/publication/374520836\_Challenges\_in\_High-Performance\_Computing