#### International Journal of Emerging Trends in Computer Science and Information Technology

ISSN: 3050-9246 | https://doi.org/10.63282/3050-9246/IJETCSIT-V6I1P102 Eureka Vision Publication | Volume 6, Issue 1, pp. 12-22, 2025

Original Article

# The Future of Heterogeneous Computing: Integrating CPUs, GPUs, and FPGAs for High-Performance Applications

Muthukumaran Vaithianathan Samsung Semiconductor Inc., San Diego, USA.

Received On: 03/01/2025

Revised On: 12/01/2025

Accepted On: 16/01/2025

Published On: 19/01/2025

Abstract - The future of heterogeneous computing is poised revolutionize high-performance applications by integrating diverse processing units such as CPUs, GPUs, and FPGAs. This integration aims to leverage the unique strengths of each architecture, enhancing computational efficiency and performance across various domains, including artificial intelligence (AI), machine learning, and scientific simulations. As workloads become increasingly complex, the demand for adaptable and flexible hardware solutions rises. Heterogeneous systems will enable the dynamic allocation of tasks to the most suitable processing unit, optimizing resource utilization and minimizing latency. Key advancements in this field include the development of unified memory architectures that facilitate seamless data sharing between CPUs and GPUs, reducing overhead and improving computational speed. Furthermore, incorporation of FPGAs offers significant advantages in energy efficiency and parallel processing capabilities, making them ideal for specific compute-intensive tasks. The trend towards System on Chip (SoC) designs is also notable, as it allows for the integration of multiple processor types within a single chip, further enhancing performance in compact environments. As research progresses, we anticipate a shift towards hierarchical heterogeneous computing systems that will not only utilize multiple architectures within a single node but also across distributed systems. This evolution will be critical in meeting the escalating demands of high-performance computing applications.

Keywords - Heterogeneous Computing, CPUs, GPUs, FPGAs, High-Performance Computing, AI Integration, Unified Memory Architecture, Energy Efficiency.

#### 1. Introduction

Heterogeneous computing refers to the use of different types of processors or cores within a single system to optimize performance and efficiency for a variety of workloads. Traditionally, computing systems relied heavily on a single type of processor, typically the Central Processing Unit (CPU). However, as applications have evolved—especially in fields like artificial intelligence (AI), machine learning, and big data analytics—the limitations of CPUs alone have become evident. This has led to a growing interest in integrating Graphics Processing Units (GPUs) and Field-Programmable Gate Arrays (FPGAs) into computing architectures.

# 1.2. The Need for Diverse Processing Units

The primary motivation behind heterogeneous computing is the distinct operational characteristics of each processing unit. CPUs are designed for general-purpose tasks and excel at sequential processing, making them ideal for tasks that require high single-threaded performance. In contrast, GPUs are optimized for parallel processing, to handle thousands of simultaneously, which is particularly beneficial for tasks such as image processing and deep learning. FPGAs offer a unique advantage by allowing developers to customize hardware configurations for specific applications, providing high efficiency and low latency. As workloads become more complex and varied, the need for a flexible computing architecture that can dynamically allocate tasks to the most suitable processor type becomes crucial. This adaptability not only enhances performance but also improves energy efficiency, which is increasingly important in data centers and edge computing environments.

## 1.3. Advancements in Heterogeneous Computing

Recent advancements in heterogeneous computing have focused on creating more cohesive systems that facilitate better communication between different processing units. Technologies such as unified memory architectures allow CPUs and GPUs to share data more efficiently, reducing the overhead associated with data transfer. Furthermore, the integration of FPGAs into heterogeneous systems has opened new avenues for accelerating specific workloads while maintaining energy efficiency. The trend towards System on Chip (SoC) designs is also noteworthy. By incorporating multiple processing units within a single chip, SoCs can deliver enhanced performance while minimizing physical space and power consumption. As these technologies continue to evolve, we anticipate significant improvements in the capabilities of heterogeneous computing systems, paving the way for more powerful and efficient high-performance applications across various industries.

## 2. State of the Art

#### 2.1. CPU Architectures

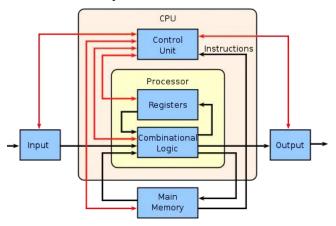

The figure represents the internal architecture of a Central Processing Unit (CPU) and its interaction with input, output, and memory subsystems. At the core of the architecture lies the Processor, which is composed of critical components such as registers and combinational logic. Registers are small, fast memory units that temporarily hold data and instructions being processed. The combinational logic performs arithmetic and logical operations, forming the foundation of computation within the CPU.

Figure 1. Internal Architecture of a CPU

Surrounding the processor is the Control Unit, which orchestrates the execution of instructions by coordinating the flow of data between the registers, memory, and other subsystems. The control unit decodes the incoming instructions and generates appropriate control signals to execute them. By directing the movement of data and instructions, the control unit ensures seamless communication between the processor and other components of the system.

The architecture also includes the Main Memory, which serves as the CPU's primary storage for programs and data. When the CPU fetches instructions from the main memory, it processes them and stores the results either back in the memory or sends them to the Output system. The arrows in the diagram indicate the data flow, with black lines representing the normal flow of information and red lines illustrating the instruction and control signal pathways. This differentiation emphasizes the CPU's dual role: data processing and control signal generation.

Another crucial feature of the architecture is its interaction with Input and Output subsystems. Input devices provide the data and instructions needed for computation, while output devices receive the processed data. The CPU acts as the central hub, managing these interactions and ensuring the system operates cohesively. This modularity allows CPUs to be used in various applications, from general-purpose computing to embedded systems. This diagram effectively encapsulates the fundamental principles of CPU architecture, emphasizing its modular design and data flow mechanisms. By illustrating the key components and their interactions, the figure provides a clear understanding of how CPUs perform computations and manage data in modern computing systems.

#### 4.2. GPU Architectures

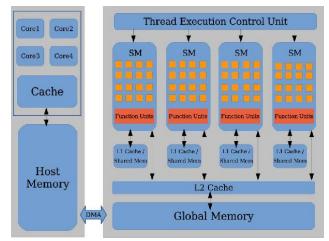

The figure illustrates the architectural design of a heterogeneous computing system that integrates CPUs and GPUs for high-performance computing tasks. The left section of the diagram represents a multi-core CPU structure, where individual cores share access to the host memory and cache. The CPU is responsible for general-purpose tasks such as sequential processing, coordination of data transfer, and task allocation to other specialized components. A Direct

Memory Access (DMA) controller ensures efficient data transfer between the host memory and other components.

Figure 2. High-Level Architecture of a Heterogeneous Computing System

On the right side, the figure showcases the GPU architecture, which is composed of multiple Streaming Multiprocessors (SMs). Each SM contains numerous function units capable of performing parallel operations. The GPU excels at executing highly parallelized workloads, such as those required for graphics rendering, deep learning, or scientific computations. The Thread Execution Control Unit coordinates threads across the function units, ensuring efficient resource utilization.

Each SM is also equipped with L1 cache or shared memory to store frequently accessed data locally, reducing latency and improving performance.

The image also highlights the memory hierarchy within the heterogeneous system. At the GPU level, L1 cache and shared memory facilitate fast, low-latency data access for the individual SMs, while the L2 cache operates as an intermediate storage layer between the SMs and the global memory. Global memory serves as the largest and slowest memory space, storing data required for execution across the GPU but requiring higher latency for access. This hierarchical memory design optimizes the performance of the system by balancing speed and capacity.

The DMA controller acts as a bridge between the CPU and GPU, facilitating seamless data transfer between the host memory and the global memory of the GPU. This is critical for heterogeneous computing systems where tasks are distributed between CPUs and GPUs based on their respective strengths. By offloading parallel tasks to the GPU and managing communication efficiently, the system achieves significant performance improvements for highperformance applications. Overall. this architecture highlights the principles of heterogeneous computing: leveraging the strengths of multiple processing units to achieve optimal performance for diverse workloads. The integration of CPUs for sequential processing and GPUs for parallel computation, coupled with a carefully designed hierarchy, demonstrates the potential memory heterogeneous systems in addressing modern computational challenges.

#### 4.3. FPGA Architectures

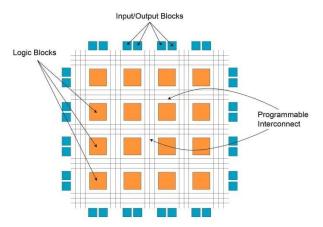

Field-Programmable Gate Arrays (FPGAs) are highly flexible and reconfigurable hardware platforms widely used in heterogeneous computing systems. The architecture of an FPGA consists of three primary components: Logic Blocks, Programmable Interconnects, and Input/Output (I/O) Blocks, which work together to enable the design and implementation of custom hardware circuits tailored for specific applications.

Figure 3. Basic Architecture of an FPGA

Logic Blocks form the core computational units of FPGAs and are responsible for implementing logic functions. These blocks typically consist of Look-Up Tables (LUTs), flip-flops, and multiplexers, which allow users to define complex combinational and sequential logic. Each logic block is designed to be highly programmable, making FPGAs well-suited for applications requiring high degrees of customization and parallelism. Programmable Interconnects provide the essential connections between logic blocks, I/O blocks, and other components. This flexible routing fabric allows for communication across the FPGA, enabling designers to implement a variety of circuit designs. The interconnects are configured using static memory cells, which determine the paths that signals take within the FPGA. The routing flexibility of programmable interconnects is a critical factor in the adaptability of FPGAs, allowing them to support diverse applications with varying performance and resource requirements.

Input/Output Blocks act as the interface between the FPGA and external devices or systems. These blocks enable data transmission to and from the FPGA, supporting communication protocols such as SPI, I2C, or Ethernet. The I/O blocks are highly configurable, supporting various voltage levels and signal standards to ensure compatibility with a wide range of devices. This modular and reconfigurable architecture makes FPGAs ideal for tasks such as real-time signal processing, hardware acceleration of machine learning algorithms, and prototyping custom hardware designs. Compared to CPUs and GPUs, FPGAs offer unparalleled flexibility and energy efficiency, albeit at the cost of higher design complexity and programming effort.

# 3. Heterogeneous Integration Strategies

# 3.1. System-Level Integration

System-level integration in heterogeneous computing is critical for ensuring that various processing units, such as

CPUs, GPUs, and FPGAs, can operate cohesively within a single framework. This integration encompasses several key components: interconnects, communication protocols, and memory hierarchies. Interconnects are the backbone of any heterogeneous system, facilitating communication between the different processors. High-speed buses and networks are employed to link these diverse components, allowing for efficient data transfer and minimizing latency. Technologies such as PCI Express (PCIe) and newer interfaces like CXL (Compute Express Link) are increasingly being utilized to enhance bandwidth and reduce bottlenecks. These interconnects ensure that data flows seamlessly between processors, enabling them to collaborate effectively on complex tasks.

Communication protocols play a vital role in managing how data is exchanged across different processors. These protocols dictate the rules for data transmission, ensuring that messages are correctly formatted and delivered. Protocols such as OpenCL and MPI (Message Passing Interface) are commonly used in heterogeneous systems to facilitate parallel processing and task delegation among CPUs and GPUs. The choice of protocol can significantly impact system performance; thus, careful selection is crucial based on the specific requirements of the applications being run. Memory hierarchies are another essential aspect of system-level integration. In heterogeneous computing environments, managing memory access efficiently is paramount due to the differing memory architectures of various processors. Unified memory architectures allow for shared memory spaces between CPUs and GPUs, enabling faster data access and reducing the overhead associated with transferring data between separate memory pools. Advanced caching strategies further enhance performance by keeping frequently accessed data close to the processing units that require it.

# 3.2. Programming Models and Frameworks

Programming models and frameworks are essential for harnessing the capabilities of heterogeneous computing systems effectively. They provide developers with the tools necessary to write software that can efficiently utilize multiple types of processors, such as CPUs, GPUs, and FPGAs. Some of the most prominent frameworks include CUDA, OpenCL, and Vitis. CUDA (Compute Unified Device Architecture) is a parallel computing platform developed by NVIDIA specifically for its GPUs. It allows developers to write software using C/C++ extensions that can execute on NVIDIA hardware. CUDA simplifies the process of offloading compute-intensive tasks from the CPU to the GPU by providing a rich set of libraries and APIs tailored for high-performance computing applications. Its widespread adoption in machine learning and scientific computing highlights its effectiveness in optimizing performance across various workloads.

OpenCL (Open Computing Language) is an open standard for parallel programming that supports a wide range of hardware platforms, including CPUs, GPUs, and FPGAs from different vendors. OpenCL provides a unified programming model that enables developers to write code once and run it on any compliant device, promoting portability across heterogeneous systems. Its flexibility allows for fine-grained control over task scheduling and

resource management, making it suitable for diverse applications from graphics rendering to complex simulations. Vitis, developed by Xilinx (now part of AMD), is a unified software platform designed specifically for FPGAs and adaptive computing systems. Vitis allows developers to leverage high-level programming languages like C/C++ or OpenCL to create applications that can be accelerated on FPGAs without requiring deep knowledge of hardware design. This abstraction layer facilitates rapid development cycles while enabling significant performance gains through hardware acceleration.

#### 3.3. Hardware-Software Co-Design

Hardware-software co-design is an approach that emphasizes the simultaneous development of hardware and software components within heterogeneous computing systems to achieve optimal performance and efficiency. This strategy recognizes that both hardware capabilities and software requirements must be aligned closely to exploit the full potential of integrated processing units like CPUs, GPUs, and FPGAs. One key aspect of hardware-software codesign is customizing hardware for software optimization. By understanding the specific computational needs of an application early in the design process, engineers can tailor hardware configurations such as selecting appropriate FPGA architectures or optimizing GPU memory bandwidth—to enhance performance characteristics. This customization often involves creating specialized processing units or accelerators designed for specific tasks or algorithms prevalent in targeted applications like deep learning or realtime data processing.

Another important component is iterative design, where feedback loops between hardware design and software development facilitate continuous improvement. For instance, profiling tools can analyze software performance on existing hardware configurations, identifying bottlenecks or inefficiencies that can inform subsequent hardware revisions. This iterative process allows designers to refine both hardware architectures and software algorithms in tandem, leading to more efficient overall system designs. Furthermore, collaborative development environments play a significant role in enabling effective co-design practices. Tools that integrate simulation capabilities with both hardware description languages (HDLs) for FPGAs and high-level programming languages for CPUs/GPUs allow teams to visualize how changes in one domain affect the other. This holistic view fosters better decision-making regarding resource allocation, scheduling strategies, and overall system architecture.

# **4.** Applications of Heterogeneous Computing *4.1. Machine Learning and AI*

Heterogeneous computing has become a cornerstone in the advancement of machine learning (ML) and artificial intelligence (AI), enabling the efficient processing of vast datasets and complex algorithms. The integration of diverse processing units CPUs, GPUs, and FPGAs allows for the optimization of various tasks inherent in ML workflows, from data preprocessing to model training and inference.

• Parallel Processing Capabilities: GPUs, with their ability to handle thousands of threads simultaneously, are particularly well-suited for training deep learning models.

Tasks such as matrix multiplications, which are prevalent in neural networks, can be executed much faster on GPUs compared to traditional CPUs. For instance, frameworks like TensorFlow and PyTorch leverage GPU acceleration to significantly reduce training times for complex models, making it feasible to work with larger datasets and more intricate architectures.

- Custom Hardware Acceleration: FPGAs offer unique advantages in ML applications by allowing developers to create custom hardware configurations tailored to specific algorithms. This flexibility enables optimizations that can lead to enhanced performance and lower power consumption. For example, companies like Xilinx provide tools that allow users to implement ML algorithms directly onto FPGAs, resulting in significant speed improvements for inference tasks in edge devices.

- Hybrid Approaches: The combination of CPUs and GPUs in a heterogeneous architecture allows for a hybrid approach where each processor type is utilized for its strengths. CPUs can manage the orchestration of tasks and handle less parallelizable workloads, while GPUs take on the heavy lifting of parallel computations. This division of labor not only improves efficiency but also enhances the overall performance of ML systems.

- Real-World Applications: In practical scenarios, heterogeneous computing is employed in various AI applications such as natural language processing (NLP), image recognition, and autonomous systems. For instance, self-driving cars utilize heterogeneous architectures where CPUs handle sensor data fusion and decision-making processes while GPUs perform real-time image processing from cameras.

# 4.2. Scientific Simulations

Scientific simulations are among the most demanding computational tasks that benefit greatly from heterogeneous computing architectures. These simulations often involve complex mathematical models that require significant processing power for accurate results. By integrating different types of processors—CPUs, GPUs, and FPGAs—scientific researchers can achieve unprecedented levels of performance and efficiency.

- Accelerated Computational Speed: Heterogeneous computing allows scientists to leverage the strengths of various processors. CPUs are adept at handling general-purpose tasks and managing complex algorithms that require high precision. In contrast, GPUs excel at performing parallel computations necessary for simulating large-scale phenomena such as climate models or molecular dynamics. For example, researchers can use multiple GPUs to run simulations that involve millions of particles or complex fluid dynamics equations, dramatically reducing computation time from weeks to days or even hours.

- Flexibility in Modeling: The ability to customize hardware configurations using FPGAs provides additional benefits for scientific simulations. Researchers can tailor FPGA designs to optimize specific algorithms or simulation parameters, enhancing both speed and efficiency. This adaptability is particularly useful in fields like astrophysics or bioinformatics, where simulation requirements may vary significantly between projects.

- Integration with Machine Learning: Recent advancements have seen the integration of machine learning techniques into scientific simulations. By employing ML models trained on simulation data, researchers can create surrogate models that approximate complex behaviors with reduced computational costs. Heterogeneous systems facilitate this integration by allowing ML algorithms to run alongside traditional simulation codes on the same hardware platform.

- Case Studies and Applications: Numerous scientific disciplines have adopted heterogeneous computing for simulations. In physics-based modeling, researchers have utilized GPU clusters to solve differential equations governing fluid dynamics or particle interactions efficiently. Similarly, in climate science, heterogeneous systems enable researchers to simulate long-term climate patterns by processing vast amounts of data from satellite observations and climate models.

#### 4.3. Image and Signal Processing

Heterogeneous computing has transformed image and signal processing by enabling faster computations and more efficient handling of large datasets. The integration of CPUs, GPUs, and specialized accelerators allows for optimized

workflows tailored specifically for processing-intensive applications such as computer vision, medical imaging, and audio signal analysis.

- Parallel Processing Advantages: Image processing tasks often involve operations that can be executed concurrently across multiple pixels or frames. GPUs are particularly effective in this context due to their architecture designed for parallelism. Tasks such as filtering, transformation, and feature extraction can be accelerated significantly when offloaded from CPUs to GPUs. For instance, real-time video processing applications such as facial recognition or object detection benefit immensely from this capability as they require rapid analysis of high-resolution frames.

- Custom Hardware Solutions: FPGAs provide an additional layer of flexibility by allowing developers to create custom hardware solutions optimized for specific image processing algorithms. This customization can lead to improved performance metrics such as reduced latency and lower power consumption compared to general-purpose processors. Applications like real-time medical imaging utilize FPGA-based systems for rapid reconstruction algorithms that enhance image quality while minimizing patient exposure to radiation.

- Frameworks and Libraries: Several programming frameworks facilitate the development of image processing applications on heterogeneous systems. Libraries such as OpenCV (Open Source Computer Vision Library) provide support for both CPU-optimized functions as well as GPU-accelerated routines through CUDA or OpenCL interfaces. This versatility allows developers to choose the best execution path based on available hardware resources while ensuring compatibility across different platforms.

- Real-World Applications: Heterogeneous computing is widely applied in various domains requiring image and signal processing capabilities. In healthcare, advanced imaging techniques like MRI or CT scans utilize

heterogeneous architectures for faster reconstruction times and improved diagnostic accuracy. In consumer electronics, smartphones employ heterogeneous systems combining CPU/GPU capabilities for camera functionalities such as HDR imaging or augmented reality effects.

#### 4.4. Big Data Analytics

The era of big data has necessitated advanced computational techniques capable of handling vast volumes of information efficiently. Heterogeneous computing has emerged as a vital solution for big data analytics by combining various processor types CPUs, GPUs, FPGAs to optimize data processing workflows across numerous applications ranging from business intelligence to scientific research.

- Enhanced Data Processing Speed: One of the primary advantages of heterogeneous computing in big data analytics is its ability to accelerate data processing tasks significantly. While CPUs are effective at managing general-purpose computations and executing complex queries on structured data sets, GPUs excel at performing parallel operations on unstructured data typically found in big data scenarios—such as images or text documents. By offloading intensive calculations like transformations aggregations or onto GPUs, organizations can achieve considerable reductions in query response times.

- Scalability through Distributed Systems:

Heterogeneous architectures also support distributed computing environments where multiple nodes equipped with different types of processors work collaboratively on large datasets. Frameworks such as Apache Spark have been optimized for heterogeneous systems; they allow users to define workflows that automatically distribute tasks based on resource availability across CPU/GPU clusters effectively managing workloads according to specific requirements.

- Machine Learning Integration: As big data analytics increasingly incorporates machine learning techniques for predictive modeling or pattern recognition tasks, heterogeneous computing provides an ideal environment where these algorithms can be executed efficiently alongside traditional analytics methods. For instance, organizations can leverage GPU acceleration during model training phases while utilizing CPU resources for data preprocessing steps a hybrid approach that optimizes overall system performance.

- Industry Applications: Various industries have adopted heterogeneous computing solutions for big data analytics purposes from finance firms analyzing market trends using real-time transaction data streams to healthcare institutions leveraging patient records combined with genomic information for personalized medicine approaches.

#### 4.5. Embedded and Real-Time Systems

Embedded systems are increasingly incorporating heterogeneous computing architectures due to their ability to meet stringent performance requirements while maintaining energy efficiency a crucial factor in many real-time applications ranging from automotive systems to IoT devices.

- Performance Optimized Characteristics: Heterogeneous computing allows embedded systems designers to select appropriate processors based on characteristics specific workload within their applications. For example, a system may utilize a lowpower CPU for general control tasks while deploying a GPU or FPGA for compute-intensive functions such as image processing or signal analysis enabling optimal resource allocation tailored specifically application demands.

- Real-Time Processing Capabilities: Many embedded applications require real-time performance guarantees where timely responses are critical for instance autonomous vehicles must process sensor inputs rapidly enough without introducing unacceptable delays into decision-making processes; here heterogeneous architectures provide an advantage by distributing workloads effectively between different processors ensuring responsiveness even under heavy loads.

- Energy Efficiency Considerations: Energy efficiency is paramount within embedded systems especially those deployed in battery-operated devices; heterogeneous architectures allow designers not only optimize performance but also minimize power consumption through dynamic task allocation strategies whereby less demanding tasks run on energy-efficient cores while more intensive calculations leverage higher-performance units when needed thus prolonging battery life without sacrificing functionality.

- Applications Across Industries: Numerous sectors leverage heterogeneous embedded systems—from smart home devices utilizing sensors coupled with machine learning accelerators analyzing user behavior patterns; industrial automation systems integrating vision-based inspection technologies powered by FPGAs alongside traditional control logic; healthcare monitoring devices employing mixed architectures ensuring timely alerts based on patient vitals analysis—all demonstrating versatility offered through these advanced designs.

# **5.** Challenges in Heterogeneous Computing

# 5.1. Power Consumption and Efficiency

Power consumption and efficiency are critical challenges in heterogeneous computing, particularly as systems become increasingly complex and energy demands rise. While heterogeneous architectures offer the potential for improved performance by leveraging different types of processors such as CPUs, GPUs, and FPGAs—managing power consumption effectively remains a significant hurdle.

• Balancing Performance and Power: One of the primary goals in heterogeneous computing is to achieve high performance while minimizing power consumption. exhibit Different processors varying power characteristics; for instance, GPUs may deliver superior performance for parallel tasks but can consume significantly more power than CPUs when not managed properly. This disparity necessitates sophisticated algorithms that can intelligently allocate workloads to the most suitable processor based on both performance requirements and energy efficiency. Achieving this balance is challenging, as it requires a deep understanding of the power-performance trade-offs associated with each processing unit.

- Dynamic Power Management: Effective power management strategies are essential for optimizing energy efficiency in heterogeneous systems. Techniques such as dynamic voltage and frequency scaling (DVFS) allow processors to adjust their operating conditions based on workload demands, leading to reduced power consumption during idle or low-utilization periods. Implementing such strategies across a heterogeneous architecture requires careful coordination to ensure that all processing units operate harmoniously without compromising overall system performance.

- Thermal Management Considerations: In addition to power consumption, thermal management is a crucial aspect of heterogeneous computing. As different processors generate varying amounts of heat, maintaining optimal operating temperatures is necessary to prevent thermal throttling and extend hardware lifespan. Efficient cooling solutions and thermal-aware scheduling algorithms can help mitigate these issues, ensuring that the system remains within safe temperature limits while maximizing performance.

- Real-World Implications: The implications of power consumption challenges extend beyond individual systems to broader applications. For example, data centers—where heterogeneous computing architectures are increasingly deployed—face significant energy costs associated with powering and cooling equipment. By optimizing power consumption through effective workload distribution and energy-efficient designs, organizations can reduce operational costs and minimize their environmental impact.

## 5.2. Scalability and Interoperability

Scalability and interoperability are significant challenges in heterogeneous computing environments, particularly as the demand for high-performance computing continues to grow. These challenges arise from the need to integrate diverse processing units while ensuring that systems can scale effectively to meet evolving computational requirements.

- Scalability Issues: Heterogeneous systems often face difficulties in scaling due to the complexity of managing multiple types of processors with different architectures and performance characteristics. As more processing units are added to a system, maintaining an efficient workload distribution becomes increasingly challenging. Load balancing becomes critical; if certain processors are overburdened while others remain underutilized, overall system performance may suffer. To address scalability issues, developers must implement sophisticated scheduling algorithms that can dynamically allocate tasks based on real-time performance metrics and resource availability.

- Interoperability Challenges: The integration of various processing units also raises interoperability concerns. Each processor type may have its own instruction set architecture (ISA), programming models, potential communication protocols, leading to compatibility issues when attempting to run applications across different hardware platforms. Ensuring seamless communication between processors standardization of interfaces and protocols that facilitate data exchange without introducing significant overhead or latency.

- Fragmentation of Development Environments: The diversity of hardware components in heterogeneous systems can lead to fragmented development environments where developers must navigate multiple tools, libraries, and drivers specific to each processor type. This fragmentation complicates the development process, increasing debugging time and limiting choices for combining hardware from different vendors. To mitigate these challenges, there is a growing need for unified programming frameworks that abstract away hardware differences while providing developers with the flexibility to optimize their applications effectively.

- Future Directions: Addressing scalability and interoperability challenges will be crucial as heterogeneous computing continues to evolve. Research efforts focused on developing standardized APIs, communication protocols, and programming models will play a vital role in enabling smoother integration of diverse processing units within a single architecture. Additionally, advancements in cloud computing and edge computing paradigms will further drive the need for scalable heterogeneous solutions capable of adapting to varying workloads across distributed environments.

#### 5.3. Programming Complexity

Programming complexity is one of the most significant challenges facing developers working with heterogeneous computing systems. The integration of multiple types of processors—each with its own architecture, instruction set, and programming model creates an environment that can be daunting for software engineers.

- Diverse Programming Models: Each type of processor in a heterogeneous system often requires different programming models. For instance, GPUs typically utilize CUDA or OpenCL for parallel programming, while CPUs may rely on traditional sequential programming paradigms or multi-threading techniques like OpenMP or pthreads. This diversity necessitates that developers possess expertise in multiple programming languages and frameworks, complicating the development process significantly.

- Increased Development Time: The complexity introduced by having multiple processing units means that writing efficient code often requires more time-consuming optimizations tailored specifically for each processor type. Developers must carefully analyze which parts of their code should run on which processor—a task that involves understanding not only the capabilities of each unit but also their limitations regarding memory access patterns and data transfer speeds.

- Debugging Challenges: Debugging applications running on heterogeneous systems presents unique difficulties due to the interactions between different processing units. Bugs may manifest differently depending on which processor executes a particular segment of code; thus, isolating issues can become complicated when dealing with multiple architectures simultaneously. Additionally, tools for debugging across different platforms may not be fully integrated or may lack features needed for comprehensive analysis.

- Need for Higher-Level Abstractions: To alleviate some

of these complexities, there is a growing emphasis on

developing higher-level abstractions that simplify

programming tasks across heterogeneous architectures.

Frameworks like TensorFlow provide abstractions that allow developers to write code without needing intimate knowledge about underlying hardware specifics; however, such frameworks often come with trade-offs regarding performance optimization capabilities.

#### 5.4. Resource Management

Resource management is a critical challenge in heterogeneous computing systems due to the need to efficiently allocate tasks among various processing units CPUs, GPUs, FPGAs and manage shared resources effectively. As workloads grow more complex and diverse, ensuring optimal utilization of available resources becomes increasingly important.

- Dynamic Task Allocation: One major aspect of resource management involves dynamically allocating tasks based on real-time performance metrics and resource availability across different processors. This requires sophisticated scheduling algorithms capable of assessing workload demands while considering factors such as processor load balancing and interconnect bandwidth constraints. Inefficient allocation can lead to bottlenecks where certain processors are overburdened while others remain idle or underutilized.

- Memory Management Challenges: Memory management poses another significant challenge within heterogeneous systems since each type of processor may have its own memory architecture with distinct access patterns. Ensuring coherent memory access across multiple processors necessitates careful design considerations regarding data placement and transfer strategies; otherwise, latency issues could arise when moving data between different memory spaces.

- Monitoring Resource Utilization: Effective resource management also requires continuous monitoring of resource utilization metrics across all components within a heterogeneous system. Tools that provide insights into how resources are being used enable administrators to make informed decisions about workload distribution or identify areas where optimizations could be made—ultimately enhancing overall system performance.

- Interoperability Concerns: The diversity inherent in heterogeneous architectures further complicates resource management efforts because each processor may have unique characteristics requiring tailored management approaches. Developing standardized interfaces for communication between components helps mitigate some interoperability issues; however, achieving seamless integration remains an ongoing challenge requiring innovative solutions.

#### 5.5. Security Concerns

Security concerns represent a significant challenge in heterogeneous computing environments due to the complexity introduced by integrating multiple types of processors with varying architectures and security models. As these systems become more prevalent across industries—from cloud data centers to edge devices—ensuring robust security measures is paramount.

• **Diverse Attack Vectors**: The integration of different processing units increases potential attack vectors that malicious actors could exploit. Each processor type may have unique vulnerabilities associated with its

architecture or firmware; thus securing an entire system requires comprehensive strategies addressing each component's specific security needs rather than relying solely on traditional perimeter defenses.

- Data Integrity Issues: Ensuring data integrity poses another challenge within heterogeneous environments where data is frequently transferred between different processors with distinct memory architectures or storage mechanisms. Inconsistent handling of data during transfers could lead not only to corruption but also unauthorized access if proper encryption methods aren't employed consistently throughout all stages from storage through transmission—to protect sensitive information adequately.

- Access Control Mechanisms: Implementing effective access control mechanisms becomes increasingly complex when dealing with multiple types of processors operating under varied security policies or protocols governing user permissions across devices within an integrated environment; this necessitates robust identity management solutions capable of enforcing consistent access controls regardless of which component processes requests at any given time.

- Compliance Considerations: Organizations utilizing heterogeneous computing systems must also navigate compliance requirements related to data protection regulations such as GDPR or HIPAA; failure to adhere could result in severe penalties alongside reputational damage stemming from breaches attributable directly back toward inadequate security measures implemented within their infrastructure designs involving diverse technologies.

# **6. Future Directions**

# 6.1. Emerging Architectures

The future of heterogeneous computing is increasingly characterized by the integration of AI-specific accelerators within diverse architectural frameworks. As computational demands grow—particularly in artificial intelligence and high-performance computing (HPC) the need for specialized hardware that can efficiently handle complex workloads becomes paramount. Emerging architectures are evolving to incorporate various processing units, including CPUs, GPUs, and dedicated AI accelerators such as Neural Processing Units (NPUs) and Application-Specific Integrated Circuits (ASICs).

- AI-Specific Accelerators: The integration of AI-specific accelerators is a key trend shaping future architectures. These accelerators are designed to optimize performance for machine learning tasks, particularly those involving deep learning models that require extensive matrix operations. For instance, NPUs are tailored for executing neural network computations, offering superior throughput and energy efficiency compared to traditional processors. This specialization allows them to handle the increasing complexity of AI models while minimizing power consumption—a critical factor in both data centers and edge devices.

- **Hierarchical Heterogeneity**: Future architectures will likely embrace hierarchical heterogeneity, where multiple levels of processing units coexist within a single system. This approach enables the combination

- different types of processors optimized for specific tasks, allowing for more efficient resource utilization. For example, within a single node, one might find CPUs managing control tasks, GPUs handling parallel providing computations, and **FPGAs** acceleration for specialized algorithms. This layered architecture not only enhances performance but also provides flexibility in adapting to evolving computational requirements.

- Unified Memory Architectures: Another significant development in emerging architectures is the adoption of unified memory systems that allow different processors to share memory spaces seamlessly. This reduces the overhead associated with data transfers between CPUs and GPUs, leading to faster computation times and improved efficiency. Technologies such as AMD's Heterogeneous System Architecture (HSA) exemplify this trend by enabling shared memory access across various processing units.

# 6.2. Advances in Software Ecosystems

Advances in software ecosystems are crucial for maximizing the potential of heterogeneous computing systems. As these systems become more complex due to the integration of diverse processing units such as CPUs, GPUs, FPGAs, and AI accelerators there is an increasing need for unified programming frameworks that simplify development and enhance interoperability among different hardware components.

- of unified Programming Frameworks: The emergence of unified programming frameworks is a significant trend aimed at reducing the complexity associated with heterogeneous computing. Frameworks like TensorFlow and PyTorch have already begun to support multi-architecture environments by providing APIs that abstract away hardware specifics while still allowing developers to optimize their applications for performance. These frameworks enable developers to write code once and deploy it across various hardware configurations without extensive modifications.

- Containerization and Virtualization: Advances in containerization technologies also play a vital role in enhancing software ecosystems for heterogeneous computing. Tools like Docker allow developers to package applications along with their dependencies into containers that can run consistently across different environments. This approach simplifies deployment on heterogeneous architectures by ensuring that applications behave identically regardless of the underlying hardware.

- Machine Learning Optimization Tools: The rise of machine learning optimization tools further supports software development in heterogeneous environments. Automated tools can analyze workloads and suggest optimal configurations or resource allocations based on real-time performance metrics. Techniques such as neural architecture search (NAS) enable dynamic adjustments to algorithms based on specific hardware capabilities, ensuring that applications run efficiently on the available resources.

- Collaboration Across Communities: Collaboration among industry stakeholders is essential for advancing software ecosystems in heterogeneous computing.

Open-source initiatives foster innovation by allowing developers from various backgrounds to contribute to shared projects aimed at improving interoperability and performance across different architectures.

# 6.3. Enhanced Interconnect Technologies

Enhanced interconnect technologies are pivotal in addressing the communication challenges inherent in heterogeneous computing systems. As these systems integrate multiple types of processors such as CPUs, GPUs, FPGAs, and specialized AI accelerators the need for high-speed, low-latency communication solutions becomes increasingly important to ensure efficient data transfer and coordination among components.

- High-Speed Communication Protocols: One of the primary advancements in interconnect technologies involves the development of high-speed communication protocols that facilitate rapid data exchange between processing units. Protocols such as PCI Express (PCIe) have become standard for connecting GPUs and other peripherals to CPUs, enabling fast data transfers essential for performance-intensive applications. Newer protocols like Compute Express Link (CXL) further enhance this capability by providing coherent memory access across multiple devices, reducing latency and improving overall system efficiency

- **Network-on-Chip** (NoC) Architectures: In many heterogeneous systems, Network-on-Chip (NoC) architectures are being employed to manage communication between various processing elements on a single chip efficiently. NoCs allow multiple data paths between cores and memory units while minimizing congestion through intelligent routing algorithms. This approach enhances scalability by enabling seamless communication as more processing units are integrated into a system.

- Low-Latency Solutions: The demand for low-latency communication solutions has led to innovations such as optical interconnects that leverage light signals instead of electrical signals for data transmission. Optical interconnects offer significantly higher bandwidth capabilities while reducing power consumption compared to traditional copper-based connections. As applications requiring real-time processing—such as autonomous vehicles or industrial automation continue to grow, low-latency interconnects will be essential for meeting stringent performance requirements.

- Future Directions: Looking ahead, continued research into interconnect technologies will focus on achieving even higher bandwidths and lower latencies while maintaining energy efficiency. Innovations such as advanced chiplet designs will enable modular architectures where multiple interconnected chips can work together seamlessly, further enhancing scalability and flexibility within heterogeneous computing environments.

#### 6.4. Autonomous Resource Allocation

Autonomous resource allocation represents a transformative direction in heterogeneous computing systems aimed at optimizing workload management through AI-driven techniques. As these systems become increasingly complex due to the integration of diverse processing units such as CPUs, GPUs, FPGAs, and specialized accelerators—

the need for intelligent resource management becomes paramount.

- AI-Driven Workload Management: By leveraging artificial intelligence algorithms, autonomous resource allocation systems can analyze real-time performance metrics and dynamically adjust resource allocations based on workload demands. Machine learning models can predict resource requirements for specific tasks or applications by analyzing historical usage patterns; this predictive capability allows systems to allocate resources proactively rather than reactively ensuring optimal performance without manual intervention.

- Dynamic Scaling Capabilities: Autonomous resource allocation enables dynamic scaling capabilities within heterogeneous environments where resources can be adjusted based on current workloads or user demands automatically. For example, cloud service providers can utilize these techniques to allocate additional GPU instances during peak usage periods while scaling down during off-peak times; this flexibility not only improves efficiency but also reduces operational costs associated with underutilized resources.

- Intelligent Load Balancing: Effective load balancing is another critical aspect facilitated by autonomous resource allocation techniques; intelligent algorithms can distribute workloads evenly across available processing units based on their current utilization levels or specific strengths ensuring no single unit becomes a bottleneck while maximizing overall system throughput.

- Future Implications: Looking forward, advancements in autonomous resource allocation will likely incorporate more sophisticated AI models capable of adapting to changing conditions within heterogeneous systems continuously; this adaptability will enhance resilience against fluctuations in workload demands while optimizing energy consumption a crucial consideration given growing environmental concerns surrounding data center operations.

#### 7. Conclusion

The evolution of heterogeneous computing represents a significant leap forward in addressing the increasing demands of modern applications across various domains, including artificial intelligence, scientific simulations, image processing, and big data analytics. By integrating diverse processing units such as CPUs, GPUs, FPGAs, and specialized AI accelerators heterogeneous systems can leverage the unique strengths of each architecture to optimize performance, enhance energy efficiency, and improve overall resource utilization. As these technologies continue to advance, they are poised to redefine the capabilities of highperformance computing. However, the journey toward fully realizing the potential of heterogeneous computing is not without its challenges. Issues related to power consumption, scalability, programming complexity, resource management, and security must be addressed to create robust and efficient systems. The development of unified programming frameworks, enhanced interconnect technologies, and autonomous resource allocation strategies will be critical in overcoming these obstacles. By fostering collaboration among industry stakeholders and encouraging open-source initiatives, the community can work together to create solutions that promote interoperability and streamline development processes.

Looking ahead, the future of heterogeneous computing will likely be characterized by emerging architectures that incorporate AI-specific accelerators and advanced software ecosystems designed to simplify programming across diverse hardware platforms. Enhanced interconnect technologies will facilitate rapid communication between processing units, while AI-driven workload management will enable autonomous resource allocation tailored to real-time demands. Together, these advancements will pave the way for more powerful and efficient computing systems capable of tackling the most complex challenges in science, industry, and beyond. In conclusion, heterogeneous computing stands at the forefront of technological innovation, offering unprecedented opportunities for performance enhancement and efficiency gains. As we continue to explore new architectures and refine our approaches to software development and resource management, we will unlock new possibilities that can drive progress across a multitude of fields. Embracing this paradigm shift will not only propel computational capabilities but also foster a more sustainable and intelligent future for computing as a whole.

# References

- [1] DigitalOcean. (n.d.). Future trends in GPU technology. Retrieved from https://www.digitalocean.com/community/conceptual-articles/future-trends-in-gpu-technology

- [2] Kumar, A. (2014). *CPU-GPU heterogeneous computing architecture*. Retrieved from https://cfaed.tu-dresden.de/files/user/akumar/pdf/isic14.pdf

- [3] EngineeGroup. (n.d.). Applications of heterogeneous computing in computational and simulation science.

Retrieved from https://www.engineegroup.us/articles/TCSIT-7-155.php

- [4] OSTI. (2015). *Heterogeneous computing for big data systems*. U.S. Department of Energy. Retrieved from https://www.osti.gov/servlets/purl/1265534

- [5] DATAVERSITY. (n.d.). Future data center heterogeneous computing. Retrieved from https://www.dataversity.net/future-data-center-heterogeneous-computing/

- [6] MosChip. (n.d.). *The rise of FPGA technology in high- performance computing*. Retrieved from https://moschip.com/blog/iot/the-rise-of-fpga-technology-in-high-performance-computing/

- [7] Intel. (2023). Our future with hierarchical heterogeneous computing. Retrieved from https://community.intel.com/t5/Blogs/Products-and-Solutions/HPC/Our-Future-with-Hierarchical-Heterogeneous-Computing/post/1495073

- [8] ResearchGate. (n.d.). *Heterogeneous computing: The future of systems*. Retrieved from https://www.researchgate.net/publication/326088580\_H eterogeneous\_Computing\_-\_The\_Future\_of\_Systems

- [9] Suman Chintala, "Next Gen BI: Leveraging AI for Competitive Advantage", International Journal of Science and Research (IJSR), Volume 13 Issue 7, July 2024, pp. 972-977, https://www.ijsr.net/getabstract.php?paperid=SR247200 93619, DOI: https://www.doi.org/10.21275/SR24720093619

- [10] Supermicro. (n.d.). *Heterogeneous computing*. Retrieved from

- https://www.supermicro.com/en/glossary/heterogeneous -computing

- [11] Patil, C. (n.d.). *The heterogeneous integration pushing the semiconductor industry*. Retrieved from https://www.chetanpatil.in/the-heterogeneous-integration-is-pushing-the-semiconductor-industry/

- [12] EMB. (n.d.). Explore heterogeneous computing. Retrieved from https://blog.emb.global/explore-heterogeneous-computing/

- [13] Wikipedia. (n.d.). Heterogeneous computing. Retrieved from https://en.wikipedia.org/wiki/Heterogeneous computing

- [14] Nature Research Intelligence. (n.d.). *Heterogeneous* computing systems. Retrieved from https://www.nature.com/research-intelligence/heterogeneous-computing-systems

- [15] LinkedIn. (n.d.). *A brief exploration of potential heterogeneous computing futures*. Retrieved from https://www.linkedin.com/pulse/amr-future-brief-exploring-potential-heterogeneous-jrp2f

- [16] ACM. (2023). *Innovations in heterogeneous architectures for AI acceleration*. Retrieved from https://dl.acm.org/doi/10.1145/3569966.3570075

- [17] Suman Chintala, Vikramrajkumar Thiyagarajan, 2023.

"Harnessing AI for Transformative Business Intelligence Strategies", ESP International Journal of Advancements in Computational Technology (ESP-IJACT) Volume 1, Issue 3: 81-96.

- [18] KAUST. (2020). Heterogeneous integration strategy: Obtaining a balance. Retrieved from https://cemse.kaust.edu.sa/events/by-type/phd-dissertation-defense/2020/07/09/heterogeneous-integration-strategy-obtaining

- [19] Frontiers in Physics. (2023). *Heterogeneous computing and physics applications*. Retrieved from https://www.frontiersin.org/journals/physics/articles/10. 3389/fphy.2023.1320450/full

- [20] ARM. (n.d.). *Heterogeneous compute*. Retrieved from https://www.arm.com/glossary/heterogenous-compute

- [21] MDPI. (n.d.). Special issues on heterogeneous computing. Retrieved from https://www.mdpi.com/journal/electronics/special\_issue s/9FRA1ZXN7N

- [22] OpenSourceForU. (2016). *The evolution of heterogeneous systems*. Retrieved from https://www.opensourceforu.com/2016/12/how-heterogeneous-systems-evolved-and-the-challengesgoing-forward/

- [23] EdgeCortix. (n.d.). *AI drives the software-defined heterogeneous computing era*. Retrieved from https://www.edgecortix.com/en/blog/ai-drives-the-software-defined-heterogeneous-computing-era

- [24] AI Accelerator Institute. (n.d.). *Improving AI inference performance with hardware accelerators*. Retrieved from https://www.aiacceleratorinstitute.com/improving-ai-inference-performance-with-hardware-accelerators/

- [25] Suman, Chintala (2024). Evolving BI Architectures: Integrating Big Data for Smarter Decision-Making. American Journal of Engineering, Mechanics and Architecture, 2 (8). pp. 72-79. ISSN 2993-2637

- [26] SECO. (n.d.). *The evolution of AI accelerators from CPUs to NPUs*. Retrieved from https://www.seco.com/blog/details/the-evolution-of-ai-accelerators-from-cpus-to-npus

- [27] Muthukumaran Vaithianathan, Mahesh Patil, Shunyee Frank Ng, Shiv Udkar, 2023. "Comparative Study of FPGA and GPU for High-Performance Computing and AI", ESP International Journal of Advancements in Computational Technology (ESP-IJACT,) Volume 1, Issue 1: 37-46.

- [28] M. Hindka, "Securing the Digital Backbone: An Indepth Insights into API Security Patterns and Practices", Computer Science and Engineering, Vol. 14, No. 2, pp. 35-41, 2024.

- [29] Chintala, S. and Thiyagarajan, V., "AI-Driven Business Intelligence: Unlocking the Future of Decision-Making," ESP International Journal of Advancements in ComputationalTechnology, vol. 1, pp. 73-84, 2023.

- [30] Kushal Walia, 2024. "Accelerating AI and Machine Learning in the Cloud: The Role of Semiconductor Technologies", ESP International Journal of Advancements in Computational Technology (ESP-IJACT), Volume 2, Issue 2: 34-41.